Coherence: A Scientific Journal A Peer- Reviewed Journal of the Science Section The Bhawanipur Education Society College Vol.1, Issue 1 (2022) 81-85

# Performance Analysis of Germanium P-Channel Junctionless FinFET for Low Power and High Performance Applications

Gourav Choudhury and Monali Sil\*

Department of Electronics, The Bhawanipur Education Society College, Kolkata 700020, West Bengal

#### **Abstract**

In this paper, the performance of germanium (Ge) p-channel Junctionless (JL) FinFET has been compared with silicon (Si) p-channel JL-FinFET. The device performance was evaluated in terms of sub-threshold swing, threshold voltage, on current, gate capacitor, intrinsic delay, power dissipation and power delay product for present technology. The use of Ge in JL-FinFET improves 64% delay over Si counterpart when both devices have the same off current at 100pA/um.

*Keywords:* Junctionless (JL) FinFET, germanium (Ge), silicon (Si), sub-threshold swing (SS), threshold voltage ( $V_{TH}$ ), on current ( $I_{ON}$ ), off current ( $I_{OFF}$ ), delay, power dissipation, power-delay-product (PDP).

## 1. Introduction

As per Moore's law [1], aggressive down scaling of device dimension of conventional metal-oxide-semiconductor field effect transistor (MOSFET) offers various problems, including the production of ultra-sharp source/drain junctions. Downscaling increases short channel effects in device which further enhances leakage current as well as power dissipation. A junctionless transistor (JLT) [2] has been developed as a solution to this problem, and it shows significant potential for future technology nodes. JLT has the same doping type and concentration in the source, channel, and drain regions, which denotes the absence of junction in such devices. In compared to its conventional counterpart, a JLT has higher short-channel immunity [3], improved drain-induced barrier lowering (DIBL) [3], lower electric field in the on-state [4], steep sub-threshold slope [5], and improved both analog [6] and digital logic [7] performances.

For further improvement, FinFET technology has come to improve the short channel immunity by increasing the gate control of conventional MOSFET. Recently, different research groups are working on different types of advanced devices to get higher performance and lower power dissipation in CMOS technology. To enhance the speed of the device, higher mobility Ge material may be used as a p-type channel material [8]. It is reported that Ge channel devices has been simply integrated into Si process technology. High drive current [9], outstanding  $I_{ON}$  to  $I_{OFF}$  ratio [10] and impressive immunity to control short-channel effects (SCEs) [11] have been already reported in Ge-on-insulator (GeOI) devices.

<sup>\*</sup> Correspondent Author: email: monali.sil@thebges.edu.in (M. Sil)

JL-FinFET on GeOI has been studied recently [12-15] in order to integrate the intrinsic qualities of Ge with the good features of JLT. Additionally Ge JL-FinFET provides better immunity against random-discrete-dopant induced threshold voltage fluctuation [16].

In this paper, we have investigated some device characteristics of Ge p-channel JL-FinFET in comparison with Si p-channel JL-FinFET. To understand and analyze the device performance of aforementioned devices, node 10nm technology of IRDS 2017 [17] has been considered.

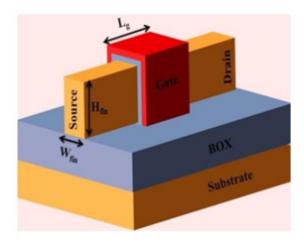

#### 2. Device structure and simulation

Sentaurus TCAD [18] has been used to simulate all the device characteristics for this study. Figure 1 shows the schematic view of JL-FinFET. As per International roadmap for device and systems (IRDS) we have chosen node 10nm technology [17] to evaluate all the device performances. The channel length is valued as 22nm, channel width as 8nm, channel height as 45nm, effective oxide thickness (EOT) as 0.9nm, doping concentration of source, channel and drain is  $4 \times 10^{19}$  atoms/cm<sup>3</sup>. The work function (WF) of gate metal for different devices has been optimized to obtain a leakage current  $I_{OFF}$  at 100 pA/ $\mu$ m in accordance with IRDS 2017. Here, 0.75V has been used as bias voltage to study the device characteristics.

Figure 1: Schematic view of JL-FinFET using TCAD simulator

Sentaurus 3D numerical device simulator [18], version H-201703.03, is used to simulate all of the device characteristics. In our simulations, doping dependent, quantum density gradient, high field saturation, normal field-dependent mobility models, quantum density gradient, Hurkx's band-to-band, Shockley–Read–Hall (SRH) recombination, and band gap narrowing (BGN) models have been used. Coulomb and neutral defect scattering effects are added with  $\mu_L$  (low-field bulk mobility) [19] for model calibration, and default values of  $\mu_L$  [20-21] are modified. The modified values of  $\mu_L$  are 80.5 and 300 m<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [22] for Si p-channel JL-FinFET and Ge p-channel JL-FinFET, respectively. All the calibrated models for Si p-channel and Ge p-channel JL-FinFETs are reported in ref. [7] against the experimental results [23].

### 3. Result and discussions

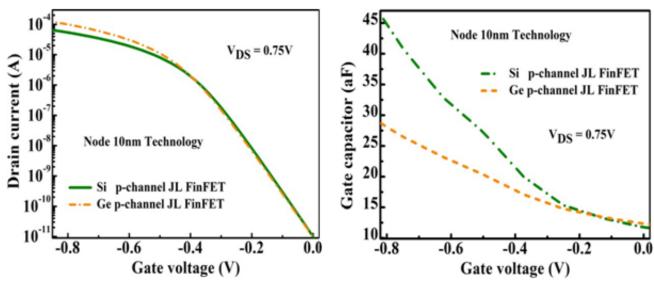

According to IRDS 2017, Figure 2 depicts the transfer characteristics (I<sub>D</sub>-V<sub>G</sub> graph) of Si p-channel and

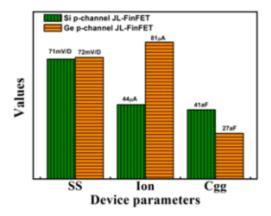

Ge p-channel JL-FinFETs for node 10nm technology. Figure 3 shows the variation of gate capacitances as a function of gate voltage using ac analysis. Figure 4 shows different device parameters for both type of devices. When  $V_{GS}=V_{DS}=0.75$  V, drive current ( $I_{ON}$ ) is calculated from Figure 2. Ge p-channel will give an 84% improvement in drive current over the Si p-channel as Ge offers higher carrier mobility than Si. Next, the Sub-threshold Swing (SS) is also calculated using the transfer characteristics and shown in Figure 4.

Figure 2: I<sub>D</sub>vsV<sub>G</sub> characteristics for both type of devices

Figure 3: C<sub>gg</sub>vsV<sub>G</sub> characteristics for both type of devices

Both devices provide nearly comparable SS, as illustrated in Figure 4. Different device parameters like threshold voltage ( $V_{\text{TH}}$ ), delay, static power dissipation ( $P_{\text{Static}}$ ), dynamic power dissipation ( $P_{\text{Dynamic}}$ ) and power delay product (PDP) are listed in Table 1. In comparison to Si p-channel JL-FinFET, Ge p-channel JL-FinFET has a slightly higher  $V_{\text{TH}}$ . As per Figure 4, it is clear that Ge provides more or less double on current and lower gate capacitance compared with Si when both devices have identical SS. As a result, Ge p-channel JL-FinFET with lower gate capacitance and higher on current provides 64% improvement in terms of intrinsic delay as intrinsic delay is measured by the CV/I metric. Thus Ge opens a path to minimize the delay of the device.

Figure 4: Different device parameters for both type of devices

Table 1: Performance parameters for both type of devices

| Parameters               | P-channel<br>Si JL-FinFet | P-channel<br>Ge JL-FinFET |

|--------------------------|---------------------------|---------------------------|

| V <sub>TH</sub> (mV)     | 333                       | 338                       |

| Delay(ps)                | 0.7                       | 0.25                      |

| P <sub>Static</sub> (pW) | 7.35                      | 7.35                      |

| $P_{Dynamic}(\mu W)$     | 33                        | 61                        |

| PDP(aJ)                  | 23                        | 15.3                      |

The static power dissipation ( $P_{\text{Static}} = I_{\text{OFF}}$ .  $V_{\text{DD}}$ ) is identical because both devices have the same off current at  $100\text{pA}/\mu\text{m}$ , however the dynamic power dissipation is different. The value of dynamic power dissipation ( $P_{\text{Dynamic}} = C_L V_{\text{DD}}^2$  f) is affected by both the load capacitor and frequency. The values of dynamic power dissipation are estimated and reflected in Table 1, assuming  $C_L = C_{\text{gg}}$  and f = 1/delay. In comparison to Si, the Ge provides lower delay and higher but it increases dynamic power dissipation. Though Ge offers higher dynamic power dissipation, the interesting part is, due to lower intrinsic delay of Ge JL-FinFET, it decreases the overall power delay product (PDP) compared with Si, as illustrated in Table-I.

#### 4. Conclusion

In comparison to Si counterparts, Ge p-channel JL-FinFETs offer higher on current, lower gate capacitance and lower delay. Sub-threshold swing, threshold voltage and static power dissipation are all the same for both types of devices. Lower delay increases dynamic power dissipation, which is a disadvantage for Ge channel devices, but overall power delay product has been reduced when utilizing Ge. Based on these findings, Ge p-channel JL-FinFETs may be an attractive higher mobility channel material for high performance and low power applications in future.

## Acknowledgement

Thanks to Prof. (Dr.) Abhijit Mallik of the Department of Electronic Science, University of Calcutta, for allowing us to use the TCAD simulation for our work.

#### References

- [1] Moore, Gordon E. "Cramming more components onto integrated circuits." *Proceedings of the IEEE* 86.1 (1998): 82-85.

- [2] Colinge, Jean-Pierre, et al. "Nanowire transistors without junctions." Nature nanotechnology 5.3 (2010): 225-229.

- [3] Lee, Chi-Woo, et al. "Performance estimation of junctionless multigate transistors." Solid-State Electronics 54.2 (2010): 97-103.

- [4] Colinge, Jean-Pierre, et al. "Reduced electric field in junctionless transistors." Applied Physics Letters 96.7 (2010).

- [5] Lee, Chi-Woo, et al. "Low subthreshold slope in junctionless multigate transistors." Applied Physics Letters 96.10 (2010).

- [6] Doria, Rodrigo Trevisoli, et al. "Junctionless multiple-gate transistors for analog applications." IEEE Transactions on Electron Devices 58.8 (2011): 2511-2519.

- [7] Guin, Shilpi, Monali Sil, and Abhijit Mallik. "Comparison of logic performance of CMOS circuits implemented with junctionless and inversion-mode FinFETs." IEEE Transactions on Electron Devices 64.3 (2017): 953-959.

- [8] C.O. Chui, K. Gopalakrishnan, P.B. Grifn, J.D. Plummer, K.C. Saraswat, Activation and diffusion studies of ion-implanted p and n dopants in germanium. Appl. Phys. Lett. 83, 3275 (2003).

- [9] Feng, Jia, et al. "P-channel germanium FinFETbased on rapid melt growth." IEEE electron device letters 28.7 (2007): 637-639.

- [10] Le Royer, C., et al. "105 nm Gate length pMOSFETs with high-K and metal gate fabricated in a Si process line on 200 mm GeOI wafers." Solid-state electronics 52.9 (2008): 1285-1290.

- [11] Van Dal, Mark JH, et al. "Germanium p-channel FinFET fabricated by aspect ratio trapping." IEEE Transactions on Electron Devices 61.2 (2014): 430-436.

- [12] Gupta, Manish, and Abhinav Kranti. "Germanium junctionless MOSFET with steep subthreshold swing." ECS Transactions 66.5 (2015): 79.

- [13] Zhao, Dan Dan, et al. "Junctionless Ge p-channel metal—oxide—semiconductor field-effect transistors fabricated on ultrathin Ge-on-insulator substrate." Applied physics express 4.3 (2011): 031302.

- [14] Zhao, Dan Dan, et al. "Experimental and analytical characterization of dual-gated germanium junctionless p-channel metal—oxide—semiconductor field-effect transistors." Japanese Journal of Applied Physics 51.4S (2012): 04DA03.

- [15] Chen, Che-Wei, et al. "Body-tied germanium tri-gate junctionless PMOSFET with in-situ boron doped channel." IEEE electron device letters 35.1 (2013): 12-14.

- [16] Nawaz, Sk Masum, Souvik Dutta and Abhijit Mallik. "Acomparison of random discrete dopant induced variability between Ge and Si junctionless p-FinFETs." Applied Physics Letters 107.3 (2015).

- [17] Moore, More. "White Paper. International Roadmap for Devices and Systems." (2016).

- [18] Guide, Sentaurus Device User, and Device User Guide. "Version N-2017.09." Mountain View, CA, USA(2017).

- [19] Jeon, Dae-Young, et al. "Low-temperature electrical characterization of junctionless transistors." Solid-State Electronics 80 (2013):135-141.

- [20] Lombardi, Claudio, et al. "Aphysically based mobility model for numerical simulation of nonplanar devices." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 7.11 (1988): 1164-1171.

- [21] Masetti, Guido, Maurizio Severi, and Sandro Solmi. "Modeling of carrier mobility against carrier concentration in arsenic, phosphorus-, and boron-doped silicon." IEEE Transactions on electron devices 30.7 (1983): 764-769.

- [22] Nazarov, Alexei, et al., eds. Semiconductor-on-insulator materials for nanoelectronics applications. Springer Berlin Heidelberg, 2011.

- [23] Barraud, S., et al. "Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm." IEEE Electron Device Letters 33.9 (2012): 1225-1227.